Design and Implementation of a Digital Clock with Alarm, and Displaying on VGA Monitor

VHDL-FPGA Project

1.PROJENİN AMAÇLARI

- Kronometreyi ve alarm saatini VGA ekranda görüntüleme

- Kullanıcıdan girişleri (kronometre, alarm ve sıfırlama) algılama

- Girişten alarm zamanını ayarlama

Giriş algılandıktan sonra kronometreyi sayma - Sinüsoidal bir düzende salınan saat yükseklikleri (bu normalde gerekli bir durum değildi, sadece görsel olarak nasıl zenginleştirilebilir olduğunu örnekledim)

- Kronometre ile alarm saatinin karşılaştırılması

- Alarm işlemi gerçekleştiğinde sesli uyarı.

Saat sistemi aşağıdaki genel gereksinimlere sahiptir:

- Düşük güç kullanmalıdır

- Üretim maliyeti düşük olmalıdır

- Yazılım mimarisi modüler olmalıdır

- Saat zamanlaması doğru olmalı, yani herhangi bir aksaklık olmamalıdır

- Tasarım, tüketilen gücü akıllıca(verimli) kullanmalıdır.

2.PROJENİN TASARIMI

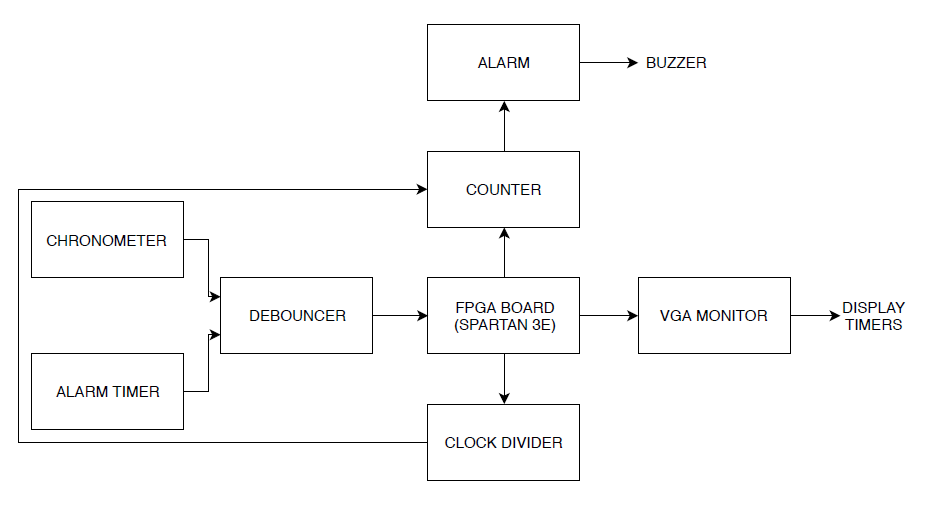

2.1 Blok Diyagramı

2.2 Projede Kullanılacak Modüller

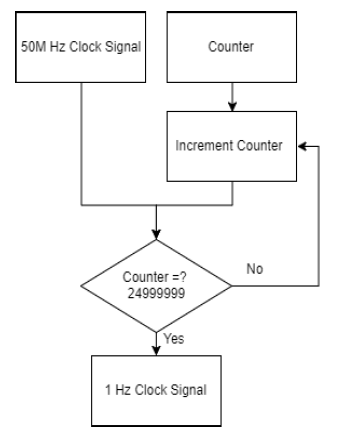

2.2.1 Clock Divider Module

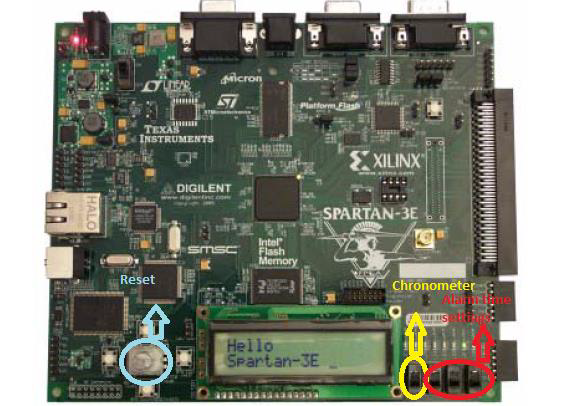

Spartan 3E kartında 50 MHz Clock Osilatörü bulunmaktadır. Yapmış olduğum projemde dijital saatler ile ilgili olduğundan, saatin düzgün çalışabilmesi ve alarmı tam zamanında çaldırması gerekiyordu. Bunun için ise Clock Sinyalini 1Hz’e düşürmem lazımdı. Ayrıca, saatlerde bulun rakamların yükseklikleri de sinüzoidal bir düzende salınmaktadır, bu salınım proje de ekstra görsellik istendiği için yapılmıştır. Bu işlemi yapmak için de yine aynı Clock sinyalini bölerek 1 Hz elde edilir. Projenin ikinci kısmında yapılan ise, elde edilen işlemlerin VGA Monitörde çıktısı alınarak gösterilmesidir. VGA sinyali üretmek için 25M Hz Clock sinyali gerekir. Sonuç olarak, bütün işlemlerin halledilip ve sistemin sorunsuz mükemmel şekilde çalıştırılması için Clock Divider Module(Saat Bölücü Modül) kullanılır.

2.2.2 Saat Bölücü Mantığı

Trigger(Tetikleme), Clock vb. sinyaller için doğru bir Pulse’a ihtiyacımız vardır. Mekanik bir cihaz olan anahtar, bastığımızda birkaç kez sıçrama (bouncing) eğilimindedir. Bu sıçramalar dijital devrelerde bir sorun olan gürültüye(noise) neden olabilir, bu sebeple anahtarın ortaya çıkardığı bu istenmeyen ani sıçramaları durdurmak için bir yöntem bulmamız gerekir. Sistemimiz Spartan 3E de bu probleme neden olan mekanik anahtarları kullanır. Bu nedenle, anahtarlarda oluşabilecek bu sıçramaları kaldırmak için, Debouncer modülünü kullandım.

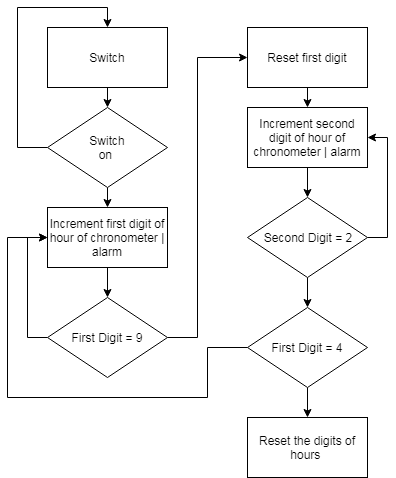

2.3 Giriş Ve Sayaç Modülleri

Projedeki giriş modülleri, kronometreyi ve alarm saatini kullanıcıdan tespit etmek için kullanılır. Kart üzerindeki anahtarlar, saati ve kronometreyi ayarlamak için kullanılır. Aşağıdaki şekilde, giriş modüllerinin ve sayaç modüllerinin nasıl çalıştığı gösterilmiştir. Kontrol anahtarı açık durumu giriş modülleri için, geri kalanı sayaç modülü içindir.

Saat Basamakları için Sayaç + Giriş Modülünün Diyagramı

Projedeki sayaç modülü, kronometre sayım işlemi için kullanılır. Saatler 1Hz’e bölünmüştür, ve bu sayede doğru çalışan bir saat gibi 1 saniyelik sürede sayım işlemi yapılır. Ayrıca sayaç modülü, zaman sınırlarına ulaştığında saniyeleri, dakikaları, saatleri kontrol eder, eğer limitlerine ulaştıysa sayaç kendini sıfırlar.

2.4 ROM Modülü

Numaraları, harfleri ve sinüsoidal dalga animasyonunu kullanarak ekranda saat göstermek için ROM kullanılmalıdır . Tasarımımdaki Karakter ROM Modülü, 32×64 olan 15 karakterden oluşmaktadır.

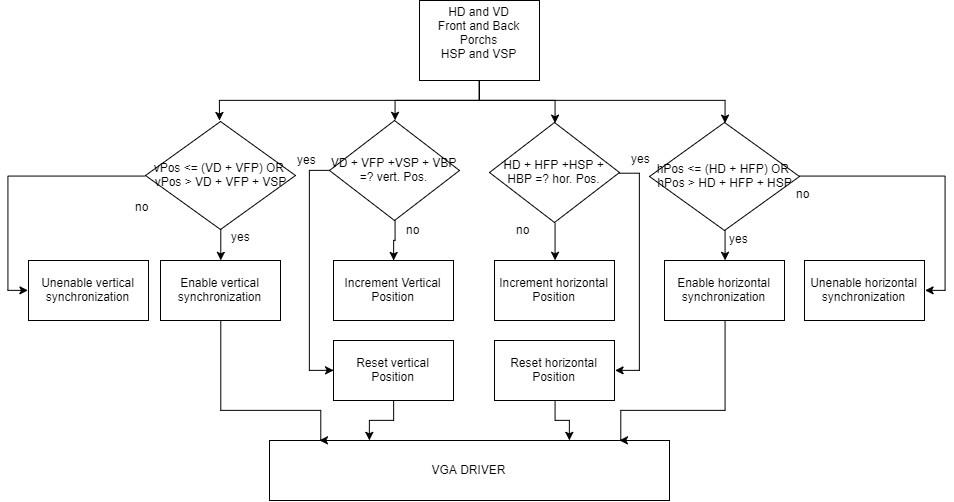

2.5. VGA Modülü

Daha önce belirttiğim gibi bu projede, kronometreyi ve alarm saatini görüntülemek için VGA modülü kullanılır. VGA modülü yatay çizgileri ve dikey çizgileri tarar ve senkronize eder. Ayrıca, gerekli konumlar eşleştiğinde, Font-ROM’dan gelen karakterler VGA monitöründe görüntülenir.

VGA Modül Diyagramı

2.6. Sinozoidal Modelleme

Sinüzoidal desen yapmak için font-ROM’da 4 faz kullandım. Bu 4 faz ile saatteki her bir basamak sıralı olmak kaydıyla yükseklikleri her saniyede salınmaktadır. Süreci daha anlaşılır hale getirmek için aşağıda gördüğünüz gibi küçük bir sinüs dalgası animasyonu ile projemizi destekledim.

4 fazlık Sinüs Pattern ROM’u

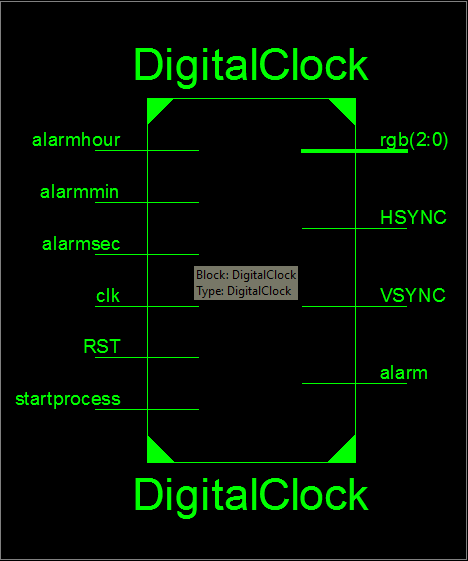

RTL Şeması

FPGA Board